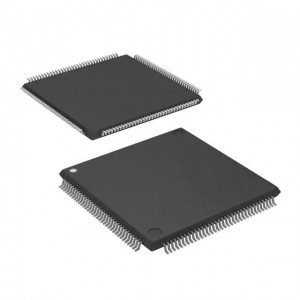

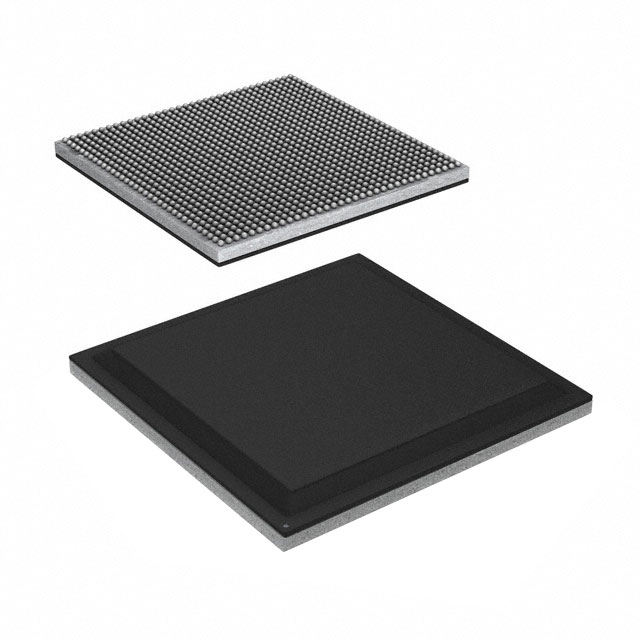

Circuito integrato nuovo e originale LCMXO2-2000HC-4TG144C

Caratteristiche del prodotto

| TIPO | DESCRIZIONE |

| Categoria | Circuiti integrati (CI)Incorporato - FPGA (array di gate programmabili sul campo) |

| Mfr | Lattice Semiconductor Corporation |

| Serie | MachXO2 |

| Pacchetto | Vassoio |

| Stato del prodotto | Attivo |

| Numero di LAB/CLB | 264 |

| Numero di elementi logici/celle | 2112 |

| Bit RAM totali | 75776 |

| Numero di I/O | 111 |

| Tensione - Alimentazione | 2,375 V ~ 3,465 V |

| Tipo di montaggio | Montaggio superficiale |

| temperatura di esercizio | 0°C ~ 85°C (TJ) |

| Pacchetto/custodia | 144-LQFP |

| Pacchetto dispositivo del fornitore | 144-TQFP (20x20) |

| Numero del prodotto base | LCMXO2-2000 |

| SPQ | 60/pz |

introduzione

Gate array programmabile sul campo, che è il prodotto di ulteriori sviluppi sulla base di dispositivi programmabili come PAL, GAL, CPLD e così via.Si presenta come un circuito semi-personalizzato nel campo dei circuiti integrati specifici per l'applicazione (ASIC), che non solo risolve le carenze dei circuiti personalizzati, ma supera anche le carenze del numero limitato di circuiti di gate del dispositivo programmabile originale.

Principio di funzionamento

L'FPGA adotta un nuovo concetto di array di celle logiche LCA (Logic Cell Array), che comprende tre parti: modulo logico configurabile CLB, modulo di ingresso di uscita IOB (Input Output Block) e connessione interna (Interconnect).Le caratteristiche di base degli FPGA sono:

1) Utilizzando FPGA per progettare circuiti ASIC, gli utenti non hanno bisogno di produrre chip per ottenere un chip adatto.

2) L'FPGA può essere utilizzato come campione pilota di altri circuiti ASIC completamente personalizzati o semi-personalizzati.

3) L'FPGA è dotato di numerosi flip-flop e pin I/O al suo interno.

4) L'FPGA è uno dei dispositivi con il ciclo di progettazione più breve, il costo di sviluppo più basso e il rischio più basso nel circuito ASIC.

5) L'FPGA adotta un processo CHMOS ad alta velocità, un basso consumo energetico e può essere compatibile con i livelli CMOS e TTL.

Si può affermare che i chip FPGA sono una delle scelte migliori per i sistemi di piccole dimensioni per migliorare l'integrazione e l'affidabilità del sistema.

L'FPGA è programmato da un programma memorizzato nella RAM su chip per impostarne lo stato operativo, quindi la RAM su chip deve essere programmata durante il funzionamento.Gli utenti possono utilizzare diversi metodi di programmazione in base alle diverse modalità di configurazione.

All'accensione, il chip FPGA legge i dati dalla EPROM nella RAM di programmazione su chip e, una volta completata la configurazione, l'FPGA entra nello stato di funzionamento.Dopo l'interruzione dell'alimentazione, l'FPGA ritorna ai fogli bianchi e la relazione logica interna scompare, quindi l'FPGA può essere utilizzato ripetutamente.La programmazione FPGA non richiede un programmatore FPGA dedicato, ma solo un programmatore EPROM e PROM generico.Quando è necessario modificare la funzione FPGA, basta cambiare la EPROM.In questo modo, lo stesso FPGA, con dati di programmazione diversi, può produrre diverse funzioni circuitali.Pertanto, l'uso degli FPGA è molto flessibile.

Modalità di configurazione

L'FPGA ha diverse modalità di configurazione: la modalità principale parallela è un FPGA più una EPROM;La modalità master-slave può supportare una PROM PEZZO che programma più FPGA;La modalità seriale può essere programmata con la PROM seriale FPGA;La modalità periferica consente di utilizzare l'FPGA come periferica di un microprocessore, programmato dal microprocessore.

Problemi come il raggiungimento di una chiusura temporale rapida, la riduzione del consumo energetico e dei costi, l'ottimizzazione della gestione del clock e la riduzione della complessità dei progetti FPGA e PCB sono sempre stati questioni chiave per i progettisti di sistemi che utilizzano FPGA.Oggi, mentre gli FPGA si spostano verso una densità più elevata, una maggiore capacità, un consumo energetico inferiore e una maggiore integrazione IP, i progettisti di sistemi beneficiano di queste prestazioni superiori affrontando nuove sfide di progettazione dovute ai livelli senza precedenti di prestazioni e capacità degli FPGA.