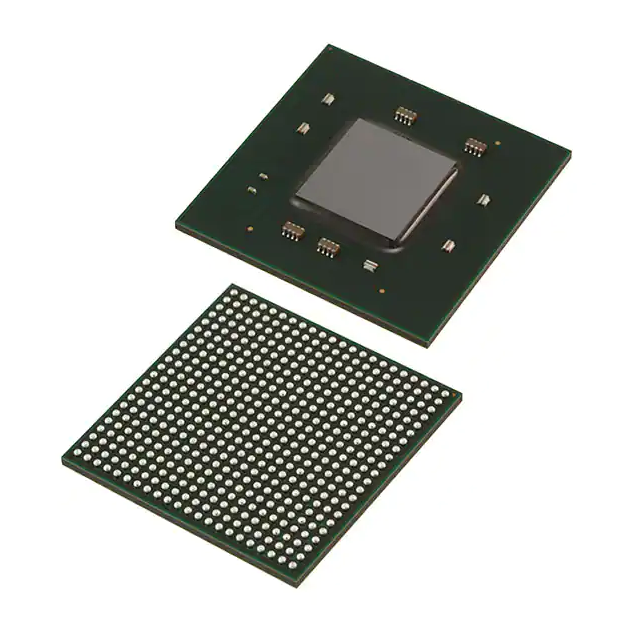

Nuovo e originale XC7A100T-2FGG484I IC circuito integrato FPGA campo programmabile Gate Array ad8313 IC FPGA 285 I/O 484FBGA

Caratteristiche del prodotto

| TIPO | DESCRIZIONE |

| Categoria | Circuiti integrati (CI)Incorporato |

| Mfr | AMD Xilinx |

| Serie | Artix-7 |

| Pacchetto | Vassoio |

| Pacchetto standard | 60 |

| Stato del prodotto | Attivo |

| Numero di LAB/CLB | 7925 |

| Numero di elementi logici/celle | 101440 |

| Bit RAM totali | 4976640 |

| Numero di I/O | 285 |

| Tensione – Alimentazione | 0,95 V ~ 1,05 V |

| Tipo di montaggio | Montaggio superficiale |

| temperatura di esercizio | -40°C ~ 100°C (TJ) |

| Pacchetto/custodia | 484-BBGA |

| Pacchetto dispositivo del fornitore | 484-FBGA (23×23) |

| Numero del prodotto base | XC7A100 |

Utilizzo di FPGA come processori di traffico per la sicurezza della rete

Il traffico da e verso i dispositivi di sicurezza (firewall) viene crittografato a più livelli e la crittografia/decrittografia L2 (MACSec) viene elaborata nei nodi di rete del livello di collegamento (L2) (switch e router).L'elaborazione oltre il livello L2 (MAC) include in genere un'analisi più approfondita, la decrittografia del tunnel L3 (IPSec) e il traffico SSL crittografato con traffico TCP/UDP.L'elaborazione dei pacchetti prevede l'analisi e la classificazione dei pacchetti in entrata e l'elaborazione di grandi volumi di traffico (1-20M) con un throughput elevato (25-400Gb/s).

A causa dell'elevato numero di risorse di calcolo (core) richieste, le NPU possono essere utilizzate per l'elaborazione di pacchetti a velocità relativamente più elevata, ma l'elaborazione del traffico scalabile a bassa latenza e ad alte prestazioni non è possibile perché il traffico viene elaborato utilizzando core MIPS/RISC e pianificando tali core in base alla loro disponibilità è difficile.L'uso di dispositivi di sicurezza basati su FPGA può eliminare efficacemente queste limitazioni delle architetture basate su CPU e NPU.

Elaborazione della sicurezza a livello di applicazione negli FPGA

Gli FPGA sono ideali per l'elaborazione di sicurezza in linea nei firewall di prossima generazione perché soddisfano con successo l'esigenza di prestazioni più elevate, flessibilità e funzionamento a bassa latenza.Inoltre, gli FPGA possono anche implementare funzioni di sicurezza a livello di applicazione, che possono ulteriormente risparmiare risorse di calcolo e migliorare le prestazioni.

Esempi comuni di elaborazione della sicurezza delle applicazioni negli FPGA includono

- Motore di scarico TTCP

- Corrispondenza delle espressioni regolari

- Elaborazione della crittografia asimmetrica (PKI).

- Elaborazione TLS

Tecnologie di sicurezza di nuova generazione che utilizzano FPGA

Numerosi algoritmi asimmetrici esistenti sono vulnerabili alla compromissione da parte dei computer quantistici.Gli algoritmi di sicurezza asimmetrici come RSA-2K, RSA-4K, ECC-256, DH ed ECCDH sono i più colpiti dalle tecniche di calcolo quantistico.Sono in fase di studio nuove implementazioni di algoritmi asimmetrici e standardizzazione NIST.

Le attuali proposte per la crittografia post-quantistica includono il metodo Ring-on-Error Learning (R-LWE) per

- Crittografia a chiave pubblica (PKC)

- Firme digitali

- Creazione chiave

L'implementazione proposta della crittografia a chiave pubblica include alcune operazioni matematiche ben note (TRNG, campionatore di rumore gaussiano, addizione polinomiale, divisione quantificatrice polinomiale binaria, moltiplicazione, ecc.).L'IP FPGA per molti di questi algoritmi è disponibile o può essere implementato in modo efficiente utilizzando elementi costitutivi FPGA, come motori DSP e AI (AIE) nei dispositivi Xilinx esistenti e di prossima generazione.

Questo white paper descrive l'implementazione della sicurezza L2-L7 utilizzando un'architettura programmabile che può essere implementata per l'accelerazione della sicurezza nelle reti edge/di accesso e nei firewall di prossima generazione (NGFW) nelle reti aziendali.