SN74ACT244PWR Buffer a 8 canali, da 4,5 V a 5,5 V con ingressi CMOS compatibili con TTL e uscite a 3 stati

Caratteristiche del prodotto

| RoHS UE | Conforme |

| ECCN (Stati Uniti) | EAR99 |

| Stato della parte | Attivo |

| HTS | 8542.39.00.01 |

| Settore automobilistico | No |

| PPAP | No |

| Famiglia logica | ATTO |

| Funzione logica | Buffer/Line Driver |

| Numero di elementi per chip | 2 |

| Numero di canali per chip | 8 |

| Numero di ingressi per chip | 8 |

| Numero di abilitazioni di input per chip | 0 |

| Numero di uscite per chip | 8 |

| Numero di abilitazioni di output per chip | 2 Basso |

| Attesa dell'autobus | No |

| Polarità | Non invertente |

| Tempo massimo di ritardo di propagazione al CL massimo (ns) | 9@4.5V to 5.5V |

| Tempo di ritardo di propagazione assoluto (ns) | 10.5 |

| Tecnologia di processo | CMOS |

| Tipo di segnale di ingresso | Single-ended |

| Tipo di uscita | 3-Stati |

| Corrente di uscita massima a basso livello (mA) | 24 |

| Corrente di uscita massima di alto livello (mA) | -24 |

| Tensione di alimentazione operativa minima (V) | 4.5 |

| Tensione di alimentazione operativa tipica (V) | 5 |

| Tensione di alimentazione operativa massima (V) | 5.5 |

| I/O tolleranti (V) | 5.5 Ingressi |

| Corrente di riposo massima (uA) | 4 |

| Condizione di test del ritardo di propagazione (pF) | 50 |

| Temperatura operativa minima (°C) | -40 |

| Temperatura operativa massima (°C) | 85 |

| Grado di temperatura del fornitore | Commerciale |

| Confezione | Nastro e bobina |

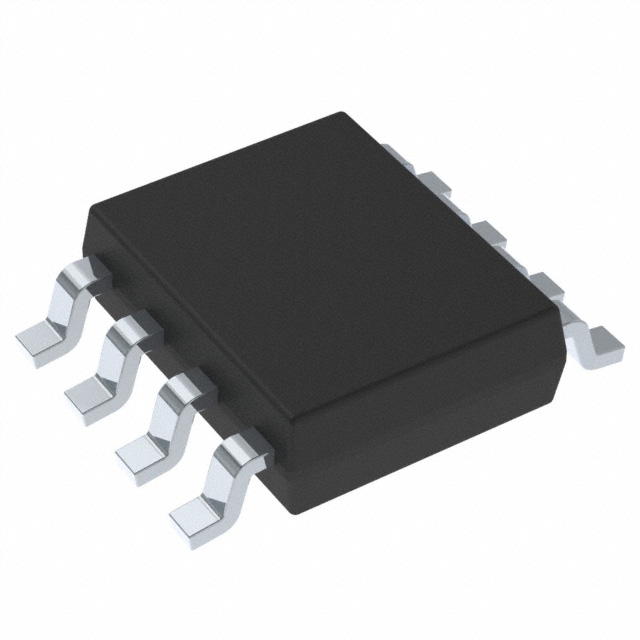

| Montaggio | Montaggio superficiale |

| Altezza del pacco | 1,05 (massimo) |

| Larghezza del pacco | 4,5 (massimo) |

| Lunghezza del pacchetto | 6,6 (massimo) |

| Il PCB è cambiato | 20 |

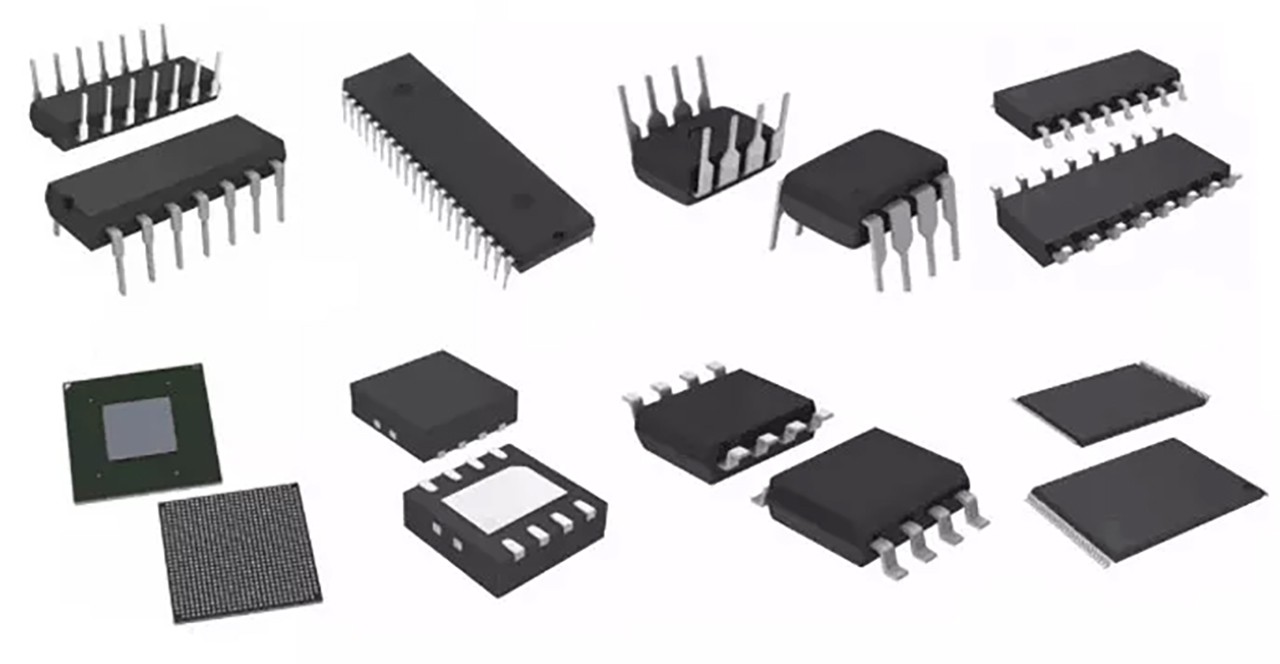

| Nome del pacchetto standard | SOP |

| Pacchetto fornitore | TSSOP |

| Conteggio pin | 20 |

| Forma del piombo | Ala di gabbiano |

Introduzione dettagliata

Questi buffer e driver ottali SNx4ACT244 sono progettati specificamente per migliorare le prestazioni e la densità dei driver degli indirizzi di memoria a 3 stati, dei driver dell'orologio e dei ricevitori e trasmettitori orientati al bus.I dispositivi SNx4ACT244 sono organizzati come due buffer e driver a 4 bit con ingressi OE (output-enable) separati.Quando OE è basso, il dispositivo trasmette dati non invertiti dagli ingressi A alle uscite Y.Quando OE è alto, le uscite sono nello stato di alta impedenza.

Scrivi qui il tuo messaggio e inviacelo