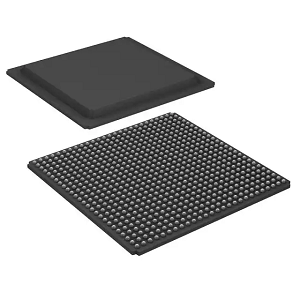

XC7Z030-2FFG676I – Circuiti integrati (CI), integrati, sistema su chip (SoC)

Caratteristiche del prodotto

| TIPO | DESCRIZIONE |

| Categoria | Circuiti integrati (CI) |

| Mfr | AMD |

| Serie | Zynq®-7000 |

| Pacchetto | Vassoio |

| Stato del prodotto | Attivo |

| Architettura | MCU, FPGA |

| Processore principale | Doppio ARM® Cortex®-A9 MPCore™ con CoreSight™ |

| Dimensione flash | - |

| Dimensioni della RAM | 256KB |

| Periferiche | DMA |

| Connettività | CANbus, EBI/EMI, Ethernet, I²C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Velocità | 800 MHz |

| Attributi primari | Kintex™-7 FPGA, celle logiche da 125.000 celle |

| temperatura di esercizio | -40°C ~ 100°C (TJ) |

| Pacchetto/custodia | 676-BBGA, FCBGA |

| Pacchetto dispositivo del fornitore | 676-FCBGA (27x27) |

| Numero di I/O | 130 |

| Numero del prodotto base | XC7Z030 |

Documenti e supporti

| TIPO DI RISORSA | COLLEGAMENTO |

| Schede tecniche | Panoramica del SoC programmabile Zynq-7000 |

| Moduli di formazione sul prodotto | Alimentazione degli FPGA Xilinx serie 7 con le soluzioni di gestione energetica di TI |

| Informazioni ambientali | Certificazione RoHS Xiliinx |

| Prodotto presentato | Tutti i SoC Zynq®-7000 programmabili |

| Design/Specifiche PCN | Modifica materiale Multi Dev 16/dic/2019 |

| Errata | Errata Zynq-7000 |

Classificazioni ambientali ed di esportazione

| ATTRIBUTO | DESCRIZIONE |

| Stato RoHS | Conformità ROHS3 |

| Livello di sensibilità all'umidità (MSL) | 4 (72 ore) |

| Stato REACH | REACH Inalterato |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Unità processore dell'applicazione (APU)

Le caratteristiche principali dell'APU includono:

• MPCore ARM Cortex-A9 dual-core o single-core.Le funzionalità associate a ciascun core includono:

• 2,5 DMIPS/MHz

• Gamma di frequenza operativa:

- Z-7007S/Z-7012S/Z-7014S (collegamento via cavo): fino a 667 MHz (-1);766 MHz (-2)

- Z-7010/Z-7015/Z-7020 (collegamento a filo): fino a 667 MHz (-1);766 MHz (-2);866 MHz (-3)

- Z-7030/Z-7035/Z-7045 (chip flip): 667 MHz (-1);800 MHz (-2);1GHz (-3)

- Z-7100 (chip flip): 667 MHz (-1);800 MHz (-2)

• Possibilità di operare in modalità processore singolo, doppio processore simmetrico e doppio processore asimmetrico

• Virgola mobile a precisione singola e doppia: fino a 2,0 MFLOPS/MHz ciascuno

• Motore di elaborazione multimediale NEON per supporto SIMD

• Supporto Thumb®-2 per la compressione del codice

• Cache di livello 1 (istruzioni e dati separati, 32 KB ciascuna)

- Set associativo a 4 vie

- Cache dati non bloccante con supporto per un massimo di quattro errori di lettura e scrittura in sospeso ciascuno

• Unità di gestione della memoria integrata (MMU)

• TrustZone® per il funzionamento in modalità sicura

• Interfaccia ACP (Accelerator Coherency Port) che consente accessi coerenti dal PL allo spazio di memoria della CPU

• Cache unificata di livello 2 (512 KB)

• Set associativo a 8 vie

• TrustZone abilitato per un funzionamento sicuro

• RAM su chip a doppia porta (256 KB)

• Accessibile tramite CPU e logica programmabile (PL)

• Progettato per l'accesso a bassa latenza dalla CPU

• DMA a 8 canali

• Supporta più tipi di trasferimento: memoria-memoria, memoria-periferica, periferica-memoria e raccolta scatter

• Interfaccia AXI a 64 bit, che consente trasferimenti DMA a throughput elevato

• 4 canali dedicati al PL

• TrustZone abilitato per un funzionamento sicuro

• Le interfacce di accesso a doppio registro impongono la separazione tra accessi sicuri e non sicuri

• Interrupt e timer

• Controller di interruzione generale (GIC)

• Tre timer watchdog (WDT) (uno per CPU e un WDT di sistema)

• Due timer/contatori tripli (TTC)

• Supporto di debug e traccia CoreSight per Cortex-A9

• Programmare la macrocella traccia (PTM) per istruzioni e traccia

• Interfaccia Cross Trigger (CTI) che consente punti di interruzione e trigger hardware