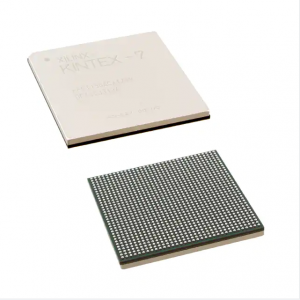

Xilinx/XC7K480T-2FFG1156I/XC7K480T/IC distinta base FPGA/circuito integrato

Specifiche

| Attributo del prodotto | Valore dell'attributo |

| Produttore: | Xilinx |

| Categoria di prodotto: | FPGA: array di gate programmabili sul campo |

| RoHS: | Dettagli |

| Serie: | XC7K480T |

| Numero di elementi logici: | 477760LE |

| Numero di I/O: | 400 I/O |

| Tensione di alimentazione – Min: | 1 V |

| Tensione di alimentazione – massima: | 1 V |

| Temperatura operativa minima: | -40 C |

| Temperatura operativa massima: | +100C |

| Velocità dati: | 12,5 Gbit/s |

| Numero di ricetrasmettitori: | 32 Ricetrasmettitore |

| Stile di montaggio: | SMD/SMT |

| Pacchetto/custodia: | FCBGA-1156 |

| Marca: | Xilinx |

| RAM distribuita: | 6788 kbit |

| Blocco RAM incorporato – EBR: | 34380 kbit |

| Frequenza operativa massima: | 640 MHz |

| Sensibile all'umidità: | SÌ |

| Numero di blocchi di array logici – LAB: | 37325LAB |

| Tensione di alimentazione operativa: | 1 V |

| Tipologia di prodotto: | FPGA: array di gate programmabili sul campo |

| Quantità nella confezione di fabbrica: | 1 |

| Sottocategoria: | CI logici programmabili |

| Nome depositato: | Kintex |

Panoramica degli FPGA XC7K480T-2FFG1156I

Descrizione generale

Gli FPGA Xilinx® serie 7 comprendono quattro famiglie FPGA che soddisfano la gamma completa di requisiti di sistema, che vanno dalle applicazioni a basso costo, con fattore di forma ridotto, sensibili ai costi e ad alto volume, alla larghezza di banda di connettività ultra high-end, alla capacità logica e alla capacità di elaborazione del segnale. per le applicazioni ad alte prestazioni più esigenti.Gli FPGA della serie 7 includono:

• Famiglia Spartan®-7: ottimizzata per costi ridotti, consumi minimi e prestazioni I/O elevate.Disponibili in confezioni a basso costo e con fattore di forma molto ridotto per un ingombro minimo sul PCB.

• Famiglia Artix®-7: ottimizzata per applicazioni a basso consumo che richiedono ricetrasmettitori seriali e DSP elevato e throughput logico.Fornisce il costo totale della distinta base più basso per applicazioni ad alta produttività e sensibili ai costi.

• Famiglia Kintex®-7: ottimizzata per il miglior rapporto qualità-prezzo con un miglioramento 2 volte rispetto alla generazione precedente, consentendo una nuova classe di FPGA.

• Famiglia Virtex®-7: ottimizzata per le massime prestazioni e capacità del sistema con un miglioramento 2 volte superiore delle prestazioni del sistema.Dispositivi con la massima capacità abilitati dalla tecnologia SSI (Stacked Silicon Interconnect).

Basati su una tecnologia di processo all'avanguardia, ad alte prestazioni, a basso consumo (HPL), a 28 nm, con gate metallico high-k (HKMG), gli FPGA della serie 7 consentono un aumento senza precedenti delle prestazioni del sistema con 2,9 Tb/ s di larghezza di banda I/O, capacità di 2 milioni di celle logiche e DSP da 5,3 TMAC/s, consumando il 50% in meno di energia rispetto ai dispositivi della generazione precedente per offrire un'alternativa completamente programmabile ad ASSP e ASIC.

Caratteristiche

• Logica FPGA avanzata ad alte prestazioni basata sulla tecnologia LUT (Lookup Table) a 6 ingressi reali configurabile come memoria distribuita.

• RAM a blocco a doppia porta da 36 Kb con logica FIFO integrata per il buffering dei dati su chip.

• Tecnologia SelectIO™ ad alte prestazioni con supporto per interfacce DDR3 fino a 1.866 Mb/s.

• Connettività seriale ad alta velocità con ricetrasmettitori multi-gigabit integrati da 600 Mb/s a velocità massime di 6,6 Gb/s fino a 28,05 Gb/s, che offre una speciale modalità a basso consumo, ottimizzata per interfacce chip-to-chip .

• Un'interfaccia analogica configurabile dall'utente (XADC), che incorpora doppi convertitori analogico-digitale da 1 MSPS a 12 bit con sensori termici e di alimentazione su chip.

• Slice DSP con moltiplicatore 25 x 18, accumulatore a 48 bit e pre-addizionatore per filtraggio ad alte prestazioni, compreso il filtraggio a coefficiente simmetrico ottimizzato.

• Potenti riquadri di gestione del clock (CMT), che combinano il loop ad aggancio di fase (PLL) e i blocchi di gestione del clock in modalità mista (MMCM) per alta precisione e basso jitter.

• Blocco integrato per PCI Express® (PCIe), per progetti fino a x8 Gen3 Endpoint e Root Port.

• Ampia varietà di opzioni di configurazione, incluso il supporto per memorie commodity, crittografia AES a 256 bit con autenticazione HMAC/SHA-256 e rilevamento e correzione SEU integrati.

• Imballaggio flipchip a basso costo, wire-bond, senza coperchio e con elevata integrità del segnale che offre una facile migrazione tra i membri della famiglia nello stesso pacchetto.Tutti i pacchetti disponibili nell'opzione Pb-free e pacchetti selezionati nell'opzione Pb.

• Progettato per prestazioni elevate e consumi minimi con processo HPL da 28 nm, HKMG, tecnologia di processo con tensione del core da 1,0 V e opzione tensione del core da 0,9 V per una potenza ancora più bassa.

La serie FPGA (Field Programmable Gate Array) Xilinx XC7K480T-2FFG1156I è FPGA, Kintex-7, MMCM, PLL, 400 I/O, 710 MHz, 477760 celle, da 970 mV a 1,03 V, FCBGA-1156, Visualizza sostituti e alternative insieme con schede tecniche, stock, prezzi dai distributori autorizzati su FPGAkey.com e puoi anche cercare altri prodotti FPGA.

Caratteristiche

Logica FPGA avanzata ad alte prestazioni basata sulla tecnologia LUT (Lookup Table) a 6 ingressi reali configurabile come memoria distribuita.

RAM a blocco a doppia porta da 36 Kb con logica FIFO integrata per il buffering dei dati su chip.

Tecnologia SelectIO ad alte prestazioni con supporto per interfacce DDR3 fino a 1.866 Mb/s.

Connettività seriale ad alta velocità con ricetrasmettitori multi-gigabit integrati da 600 Mb/s a velocità massime di 6,6 Gb/s fino a 28,05 Gb/s, che offre una speciale modalità a basso consumo, ottimizzata per interfacce chip-to-chip.

Un'interfaccia analogica configurabile dall'utente (XADC), che incorpora doppi convertitori analogico-digitale da 1 MSPS a 12 bit con sensori termici e di alimentazione su chip.

Slice DSP con moltiplicatore 25 x 18, accumulatore a 48 bit e pre-addizionatore per filtraggio ad alte prestazioni, compreso il filtraggio dei coefficienti simmetrici ottimizzato.

Potenti riquadri di gestione del clock (CMT), che combinano blocchi di clock ad aggancio di fase (PLL) e di gestione del clock in modalità mista (MMCM) per alta precisione e basso jitter.

Blocco integrato per PCI Express (PCIe), per progetti fino a x8 Gen3 Endpoint e Root Port.

Ampia varietà di opzioni di configurazione, incluso il supporto per memorie commodity, crittografia AES a 256 bit con autenticazione HMAC/SHA-256 e rilevamento e correzione SEU integrati.

Imballaggio flipchip a basso costo, wire-bond, senza coperchio e con elevata integrità del segnale che offre una facile migrazione tra i membri della famiglia nello stesso pacchetto.Tutti i pacchetti disponibili nell'opzione Pb-free e pacchetti selezionati nell'opzione Pb.

Progettato per prestazioni elevate e consumo minimo con processo HPL da 28 nm, HKMG, tecnologia di processo con tensione core da 1,0 V e opzione tensione core da 0,9 V per una potenza ancora inferiore.